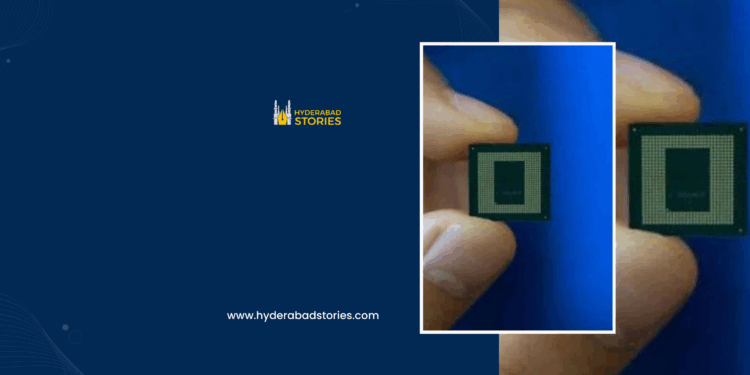

Hyderabad: In a notable stride toward advancing indigenous semiconductor innovation, Osmania University (OU), in collaboration with Chaitanya Bharathi Institute of Technology (CBIT), has successfully developed and fabricated a prototype of an all-Digital Phase-Locked Loop (ADPLL) ASIC chip under the Government of India’s Chips to Startup (C2S) programme.

The ADPLL chip, designed using 180 nm CMOS technology, was fabricated at the Semiconductor Laboratory (SCL) in Mohali — marking a key milestone in India’s push for self-reliance in chip design and manufacturing.

Hyderabad: In a milestone moment for India’s semiconductor journey, Osmania University (OU) Vice Chancellor Prof. Kumar Molugaram formally unveiled the prototype ADPLL chip on Friday. The event was attended by members of the Academic Council, senior university officials, Prof. P. Chandra Sekhar (Principal, UCEOU), and Prof. A. Krishnaiah (Dean, Faculty of Engineering), among others.

Prof. Molugaram praised the project team, led by Prof. P. Chandra Sekhar, for not only securing a ₹5 crore research grant but also for establishing the Centre of Excellence in Artificial Intelligence and Integrated Circuits (CIIC) at OU — a major initiative driving advanced research in chip design and AI.

Prof. Chandra Sekhar extended his thanks to the Ministry of Electronics and Information Technology (MeitY) and CDAC for their vital support through access to high-end Electronic Design Automation (EDA) tools like Cadence and Synopsys, and for enabling the chip’s fabrication process.

The all-digital Phase-Locked Loop (ADPLL) chip, developed under the Chips to Startup (C2S) programme, is expected to serve future high-speed digital synchronization applications. This achievement underscores the growing capabilities of India’s semiconductor ecosystem and OU’s rising leadership in next-gen electronics research.